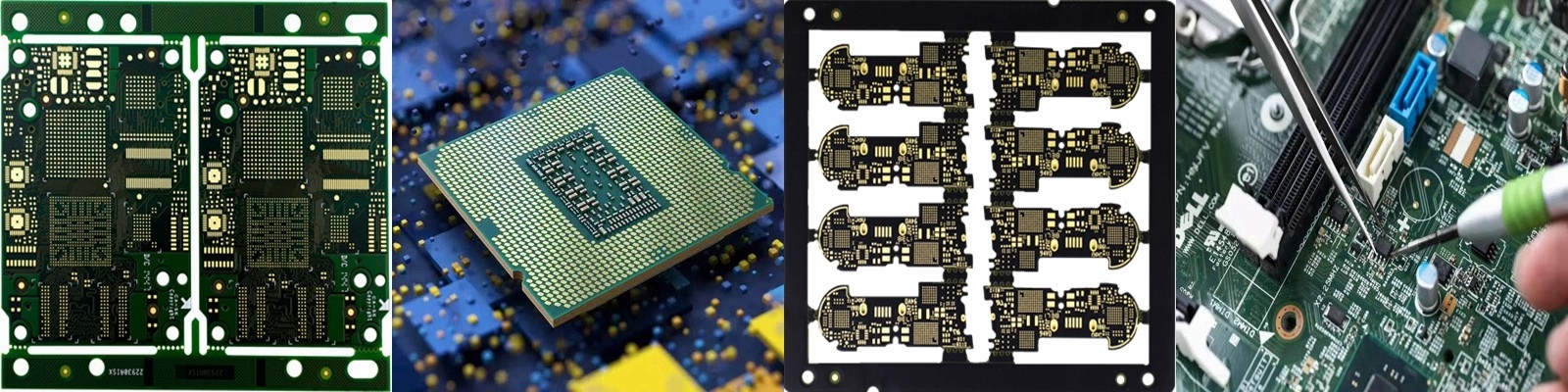

2 camadas FR4 imprimiram a placa de circuito 0,8 milímetros de espessura usada na baliza

- Características principais:

1 2 placa de circuito impresso material da carcaça da camada FR4.

O cobre de 2 duplas camada, a espessura de cobre é 35um/35um.

A espessura terminada 3 do PWB é 1.2mm.

O tamanho do desenho do PWB 4 é 128.82mm*96.14mm/6pcs

Tratamento do ouro de 5 imersões

6 PWB de 2 camadas com 6/6mil linha mínima espaço e largura.

Máscara verde da solda 7 e silkscreen branco.

Cliente de 8 necessidades para enviar-nos o arquivo do gerber ou o arquivo do PWB

| NÃO |

Artigo |

Capacidade |

| 1 |

Contagem da camada |

1-24 camadas |

| 2 |

Espessura da placa |

0.1mm-6.0mm |

| 3 |

Placa terminada Max Size |

700mm*800mm |

| 4 |

Tolerância terminada da espessura da placa |

+/--10% +/--0,1 (<1> |

| 5 |

Urdidura |

<0> |

| 6 |

Tipo principal de CCL |

KB/NanYa/ITEQ/ShengYi/Rogers Etc |

| 7 |

Tipo material |

FR4, CEM-1, CEM-3, de alumínio, de cobre, cerâmico, PI, ANIMAL DE ESTIMAÇÃO |

| 8 |

Diâmetro de furo da broca |

0.1mm-6.5mm |

| 9 |

Mergulhe para fora a espessura de cobre |

1/2OZ-8OZ |

| 10 |

Espessura interna do cobre da camada |

1/3OZ-6OZ |

| 11 |

Prolongamento |

10:1 |

| 12 |

Tolerância do furo de PTH |

+/-3mil |

| 13 |

Tolerância do furo de NPTH |

+/-1mil |

| 14 |

Espessura de cobre da parede de PTH |

>10mil (25um) |

| 15 |

Linha largura e espaço |

2/2mil |

| 16 |

Min Solder Mask Bridge |

2.5mil |

| 17 |

Tolerância do alinhamento de máscara da solda |

+/-2mil |

| 18 |

Tolerância da dimensão |

+/-4mil |

| 19 |

Max Gold Thickness |

200u' (0.2mil) |

| 20 |

Choque térmico |

288℃, 10s, 3 vezes |

| 21 |

Controle da impedância |

+/--10% |

| 22 |

Capacidade do teste |

Minuto 0.1mm do tamanho da ALMOFADA |

| 23 |

Minuto BGA |

7mil |

| 24 |

Tratamento de superfície |

OSP, ENIG, HASL, chapeando o ouro, o óleo do carbono, a máscara etc. de Peelable |

Q1: Que é os testes de esforço da interconexão do PWB (ISTs)?

A1: Os testes de esforço da interconexão do PWB (ISTs) são um processo para identificar falhas nos vias e multilayer interconectam consistentemente monitorando variações da resistência. Isto que testa é executado em um vale do teste do PWB, onde se submeta a diversos ciclos térmicos. Estes ciclos térmicos são criados aplicando atual a um vale específico do teste. As ISTs são uma maneira de verificar a confiança da placa do PWB. Este processo avalia ambos os vias e multilayer interconecta. Através dos tambores e das junções internas da camada estão expostos à corrente repetitivamente até que a falha não esteja identificada. Pode ser executada facilmente dentro das variações da temperatura de 25 a 150 graus Célsio. O motriz de testes das ISTs é verificar se o projeto da placa seja responsável para a falha.

A confiança significa como eficientemente uma placa do PWB pode executar suas funções desejadas sob circunstâncias indicadas. Os testes das ISTs são importantes para todos os níveis, dos fabricantes do PWB, montadores para utilizadores finais. Este método é registrado no IPC sob o regulamento IPC-TM-650. É usado para caracterizar o total interconecta em um PWB e detecta quebras da separação entre a camada interna através do tambor.

Vantagens do teste do PWB das ISTs

- As ISTs são mais rápidas, eficazes na redução de custos e oferecem a análise e a interpretação simplificadas.

- Repetível e reprodutível

- Identifica a falha em fases adiantadas da fabricação

- Ajudas para calcular a esperança de vida de um PWB

- Favorável ao meio ambiente

Metodologia das ISTs

O sistema das ISTs é projetado monitorar a capacidade do PWB interconecta para suportar o esforço térmico ao executar uma aplicação do fim. Pode ser executado em duas fases, no PWB manufaturado ou no montado. Em curto, ajuda a identificar para degradar a taxa de interconecta. A diferença entre os valores da resistência antes e depois de que os testes são calculados para ciclos térmicos diferentes de modo que um critério o melhor da rejeção possa ser concluído. A metodologia das ISTs permite que o usuário determine quando um defeito começa se tornar e sua taxa da propagação.

Durante testes, o sistema das ISTs aplica uma corrente da C.C. ao vale do PWB. Esta corrente aumenta a temperatura do metal e de seus materiais adjacentes. A temperatura a ser aplicada ao vale é diretamente proporcional à resistência total e à quantidade de corrente passadas através das trilhas, das almofadas, e dos furos. O sistema das ISTs mantém-se em levantar a temperatura até que alcance 150 graus Célsio (que está levemente abaixo da temperatura de transição de vidro da matéria-prima). Uma vez que a temperatura desejada conseguida, ele para o atual e refrigerar forçado começa. Isto resume o primeiro ciclo. Após isto, os monitores de sistema para a variação da resistência tendo por resultado através do rachamento ou a falha da camada interna interconectam.

O sistema de testes das ISTs mantém-se repetir este processo até que o critério determinado ‐ da rejeção esteja conseguido pre. A rejeção do vale pode ser baseada em um número máximo de ciclos, ou em um aumento da porcentagem dentro de cada resistência elevado dos circuitos dos interconnects (geralmente um aumento de 10% da resistência começando). Se a qualidade da interconexão é boa, a seguir pode sobreviver em torno das centenas de tais ciclos térmicos.

Por favor verifique seu email!

Por favor verifique seu email! Por favor verifique seu email!

Por favor verifique seu email!  Por favor verifique seu email!

Por favor verifique seu email! Por favor verifique seu email!

Por favor verifique seu email!